# NANOTEST

# NT20-3k-FC

### Description

The NT20-3k Thermotest Chip is designed as a modular system to provide the maximum of flexibility for thermal characterization and qualification of materials, packages, and systems.

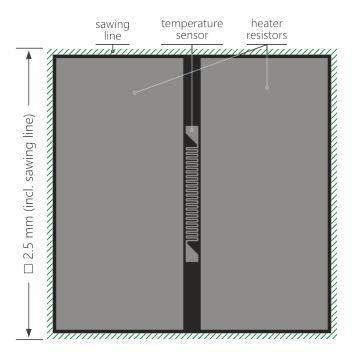

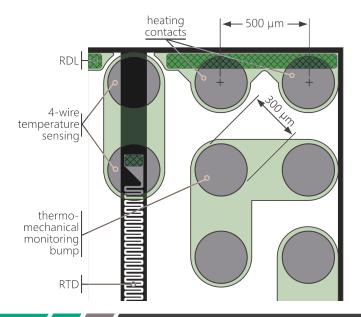

Each chip cell of  $2.5 \times 2.5 \text{ mm}^2$  size provides two uniform heaters and a centered thermistor, both connected to a large solder ball matrix for flip chip assembly via a robust redistribution layer (RDL). The solder ball matrix additionally provides solder balls explicitly dedicated to health monitoring and thermo-mechanical and reliability investigation.

The chip can be configured in any desired matrix. Temperature sensors, heaters and monitoring solder balls are each addressable individually for maximum flexibility in sensing resolution and heat distribution.

# **Technical Specification**

#### Technology and Methodology

|                           |          | ,,                  |                  |

|---------------------------|----------|---------------------|------------------|

| Fabrication tech          | nnology  | Thin                | Film             |

| Assembly techn            | ology    | Flip o              | chip             |

| Sensor                    |          | Resistance th       | ermometer        |

|                           |          |                     |                  |

| Wafer                     |          |                     |                  |

| Wafer material            |          | Silicon, u          | ndoped           |

| Wafer size                |          | 200                 | mm               |

| Wafer thickness           |          | 500                 | μm               |

| Cell size                 |          | 2.4 × 2.4           | mm²              |

| Scribe line between cells |          | 100                 | μm               |

| Topside passivat          | tion     | 7 µm Pi (polym      | er passivation)  |

|                           | option A | NiV 300 nm   Pt 10  | 0 nm   Au 100 nm |

| Backside metal            | option B | Ti 100 nm   NiV 300 | ) nm   Au 200 nm |

|                           | option C | nc                  | n                |

| Unit Cell count           |          | 440                 | 00               |

|                           |          |                     |                  |

| Heater                    |          |                     |                  |

| Heater type               |          | Resis               | stor             |

| Resistors per ch          | ip       | 2                   |                  |

| Resistors per chip      | 2        |                   |

|-------------------------|----------|-------------------|

| Resistance per resistor | 14 ± 1   | Ω                 |

| Max current per heater  | 1.5      | А                 |

| Max power per cell      | 63       | W                 |

| Max power density       | 10       | W/mm <sup>2</sup> |

| Active heater area      | 82% of c | ell area          |

#### Sensor

| Sensor type             | meander-struct | tured resistor |

|-------------------------|----------------|----------------|

| Sensor position         | cell ce        | nter           |

| Sensor connection       | 4-wire terr    | mination       |

| Resistance value (25°C) | 3.2 ± 0.1      | kΩ             |

| Sensitivity             | 10.0 *         | Ω/Κ            |

| Dimensions (I × w)      | 820 × 100      | μm²            |

|                         |                |                |

#### Assembly

| Assembly technology      | Flip | chip   |

|--------------------------|------|--------|

| Solder type              | SAG  | 2305   |

| Under bump metallization | NiAu | (4 µm) |

| Solder bump diameter     | 300  | μm     |

| Pad raster               | 500  | μm     |

theoretical value based on the Ti temperature coefficient

## Thermo-mechanical monitoring

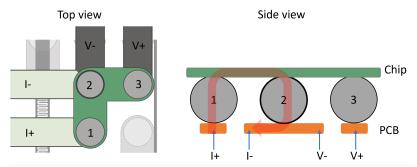

The center bump in each thermo-mechanical monitoring structure as depicted on the right (marked with a bold stroke), can be electrically monitored using 4-wire termination in a configuration as shown. The state of health correlates with the measured electrical resistance.

# **Pin configuration**

For absolute coordinates of each pin the point of origin (X=0, Y=0) is the cell center. Nomenclature is involving a prefixed letter which indicates the purpose of the specific pin. H0 and H1 pins connect to heating structures, SI to the sensor current input and SV sensor voltage sensing. TM0, TM1, TM2 and TM3 are connected to the thermo-mechanical monitoring structures.

|    | Connection | Χ [μm] | Υ [µm] |

|----|------------|--------|--------|

| A1 | H0_0       |        | 1000   |

| A2 | TMØ        |        | 500    |

| A3 | TMØ        | -1000  | 0      |

| A4 | TM1        |        | -500   |

| A5 | H0_1       |        | -1000  |

| B1 | H0_0       |        | 1000   |

| B2 | TMØ        |        | 500    |

| B3 | TM1        | -500   | 0      |

| B4 | TM1        |        | -500   |

| B5 | H0_1       |        | -1000  |

| C1 | SI_0       |        | 1000   |

| C2 | SV_0       | 0      | 500    |

| C4 | SV_1       | 0      | -500   |

| C5 | SI_1       |        | -1000  |

| D1 | H1_0       |        | 1000   |

| D2 | TM2        |        | 500    |

| D3 | TM2        | 500    | 0      |

| D4 | TM3        |        | -500   |

| D5 | H1_1       |        | -1000  |

| E1 | H1_0       |        | 1000   |

| E2 | TM2        |        | 500    |

| E3 | TM3        | 1000   | 0      |

| E4 | TM3        |        | -500   |

| E5 | H1_1       |        | -1000  |

# Chip selection guide

The length of the chip edge can be calculated depending on the number of cells per row and column using the following equation.

```

Edge length = n × cell length - scribe line length

Edge length = n × 2.5 mm

Example: (4 x 4 matrix of cells)

Edge length = 4 x 2.5 mm

Edge length = 4 x 2.5 mm

Chip size = 9.9 x 9.9 mm<sup>2</sup>

```

# Application remarks

The offered products are supposed to be used for characterization purposes. The application of the data from the test die to a functional system lies in the responsibility of the user. Nanotest makes no warranty, express or implied including the implied warranties of merchantability and fitness for a particular purpose, that the user's system designed using that data will perform as intended.

NANOTEST

Page 2 / 2 © 2023 Nanotest. All rights reserved NT20-3k-FC datasheet document rev.73